# Systematic Investigation of Metal Gates on Atomic-Layer-Deposited HfO<sub>2</sub>

Hyundoek Yang and Hyunsang Hwang\*

Department of Materials Science and Engineering, Gwangju Institute of Science and Technology, Gwangju 500-712, Korea

For *n*-type metal-oxide-semiconductor devices with HfO<sub>2</sub>, a metal gate with a very low workfunction is necessary. However, the Fermi level pinning effect shifts an effective workfunction  $\Phi_{m,eff}$  of the metal on HfO<sub>2</sub> towards a midgap value. In this paper, we systematically evaluate the  $\Phi_{m,eff}$  values of various metal gates on atomic-layer-deposited HfO<sub>2</sub> with and without surface treatments. Using high-pressure wet post-deposition-annealing (1-step process) or a wet-solution treatment after conventional post-deposition-annealing (2-step process), we could dramatically reduce the extrinsic pinning. The effective workfunction of ScN<sub>x</sub> gates on the surface-treated HfO<sub>2</sub> was ~4 eV, similar to that of the ScN<sub>x</sub>/SiO<sub>2</sub> samples. Therefore, ScN<sub>x</sub> metal gate is a good candidate for atomic-layer-deposited HfO<sub>2</sub>.

Keywords: metal gate, high-k, dielectric, MOS, pinning, workfunction, ScN, high pressure

### **1. INTRODUCTION**

The scaling of equivalent oxide thickness (EOT) is the most important issue in the development of metal-oxidesemiconductor field effect transistor (MOSFET) devices. Compared with SiO<sub>2</sub>, transition metal oxides with high dielectric constants (high-k) have an enormous advantage in EOT scaling with lower leakage current<sup>[1]</sup>. HfO<sub>2</sub> is a representative candidate for the next generation MOSFET devices, due to its high dielectric constant and excellent thermodynamic stability<sup>[2]</sup>. The metal gates, especially with low workfunction values for *n*-type MOS (NMOS) devices, are another important issue. Metal gates have been introduced to replace the conventional poly-Si gate which shows high sheet resistance, boron penetration, and Fermi level pinning (FLP), as well as an increase of EOT due to gate depletion<sup>[3]</sup>. The FLP effect of metal gates is not clearly understood yet, particularly with respect to whether the effect depends on dielectrics<sup>[4-8]</sup>. The suggested FLP consists of intrinsic FLP and extrinsic FLP. The intrinsic FLP is originated by the generation of charged dipole near at intrinsic interface states on high-k gate dielectrics<sup>[4]</sup>. The extrinsic FLP is generated by the extrinsic surface states related to chemical bonding and oxygen vacancies<sup>[9-15]</sup>. The chemical bonding between Si atoms in poly-Si or fully-sillicide (FUSI) gate and Hf atoms in HfO2 results in a shift of the effective workfunction  $(\Phi_{m,eff})$  toward a midgap value<sup>[9-11]</sup>. The oxygen vacancies caused by oxygen transport across the metal/dielectric interface are also an important factor of the extrinsic FLP<sup>[13-15]</sup>.

For NMOS or dual metal gates, various materials have been evaluated. Compared with nitride and silicide metal gates, pure metal gates offer low resistivity. However, NMOS-compatible pure metals have very low electronegativity values and result in reactions with dielectrics. The Hf gate on SiO<sub>2</sub> reduces the underlying SiO<sub>2</sub> and generates high-k dielectrics near the gate/dielectric interface<sup>[16]</sup>. The Ti gate on the HfO<sub>2</sub>/SiO<sub>2</sub> stack reduces the interfacial SiO<sub>2</sub> layer without any interaction between Ti and HfO<sub>2</sub><sup>[17]</sup>. Metal alloys such as Ru-Ta, Pt-Ta, and Ni-Ti have been suggested for dual-metal gates by using a p-type-MOS (PMOS)-compatible metal and an NMOS-compatible metal<sup>[18-20]</sup>. However, the alloys may have limited use due to the reactive NMOS-compatible pure metal. To overcome the poor thermal stability and the difficulty of controlling the EOT when using reactive pure metals, various metal compounds have been evaluated. It has been reported that a ZrN gate on HfSiON has an NMOS-compatible  $\Phi_{m,eff}$  of ~4.25 eV<sup>[21]</sup>. However, most binary metal nitrides including TaN<sub>x</sub>, TiN<sub>x</sub>, and  $HfN_x$  are not appropriate for NMOS devices<sup>[22-24]</sup>. It has been reported that the  $TaSi_xN_y$  gate is a promising NMOScompatible candidate with a  $\Phi_{m,eff}$  value of about 4.3~4.6 eV<sup>[6,25,26]</sup>. The lanthanide-incorporated metal nitrides on SiO<sub>2</sub> have NMOS-compatible  $\Phi_{m,eff}$  values<sup>[27]</sup>. In addition to nitrides, both boride and carbide can be NMOS candidates. LaB<sub>6</sub> is an NMOS-compatible gate on SiO<sub>2</sub>, but shows significant extrinsic FLP for devices with  $HfO_2^{[5]}$ . A TaC<sub>x</sub> gate on HfO<sub>2</sub> having an NMOS-compatible  $\Phi_{m,eff}$  value of

<sup>\*</sup>Corresponding author: hwanghs@gist.ac.kr

~ 4.18 eV has also been reported<sup>[5]</sup>.

In this paper, we systematically evaluate the  $\Phi_{m,eff}$  values of various metal gates on atomic-layer-deposited (ALD) HfO<sub>2</sub> with and without surface treatment. Oxygen passivation of the HfO<sub>2</sub> surface by high-pressure wet post-deposition-annealing (HP-wet-PDA) and wet-solution treatments dramatically reduces the extrinsic FLP for metal with a very low workfunction value.

#### 2. EXPERIMENTS

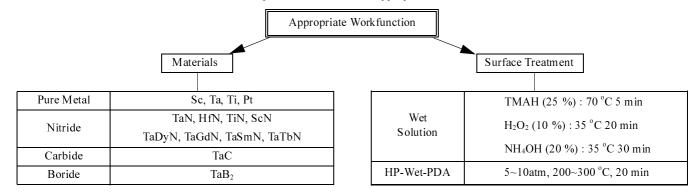

Using the ALD process, we deposited HfO<sub>2</sub> films with different thicknesses on 8-inch Si wafers with ultrathin SiO<sub>2</sub> interfacial layers. We evaluated various metal gates and surface treatments of HfO<sub>2</sub>, as summarized in Table 1. Binary metal nitrides ( $TaN_x$ ,  $HfN_x$ ,  $TiN_x$ , and  $ScN_x$ ) were deposited by reactive sputtering with various N<sub>2</sub> gas flow rates. To evaluate the effect of impurities such as B, C, and N, we used Ta-based sputter targets (TaB<sub>2</sub>, TaC, and TaN). In addition, TaC<sub>x</sub> gates were deposited by reactive sputtering with various CH<sub>4</sub>/Ar gas flow rates. Lanthanide-incorporated metal nitrides were deposited by co-sputtering of the TaN target with lanthanide elements (Dy, Gd, Sm, and Tb). In order to prevent oxidation of the surface, all metal gates were capped with 200 nm-Pt without breaking the vacuum condition. The base pressure and working pressure of the used rf magnetron sputtering system were  $\sim 5 \times 10^{-7}$  Torr and  $\sim 1 \times 10^{-3}$  Torr, respectively. To reduce the oxygen vacancies on HfO<sub>2</sub>, some samples were surface-treated before depositing the gates. The surface treatments comprised HP-wet-PDA and wet solutions such as tetramethyl ammonium hydroxide (TMAH), hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>), and ammonium hydroxide (NH<sub>4</sub>OH). The conventional PDA was performed in O<sub>2</sub> ambient at 450 °C for 30 min except for the HP-wet-PDA samples. For all the samples, post-metallization annealing in forming gas ambient (FG-PMA) was performed. The area of gates and the substrate concentration are  $2.5 \times 10^{-5}$  cm<sup>2</sup> and  $\sim 1 \times 10^{15}$  cm<sup>-3</sup>, respectively.

The physical thicknesses of  $HfO_2(T_{HfO_2})$  were determined

by X-ray reflectivity (XRR). The electrical characteristics including capacitance-voltage (C-V), conductance-voltage (G-V) and current-voltage (I-V) characteristics were evaluated using a HP 4284A Precision LCR Meter and a HP 4155A Semiconductor Parameter Analyzer. The EOT and flat-band voltage (V<sub>fb</sub>) values of the MOS devices were extracted by the Berkeley simulator<sup>[28]</sup>. The  $\Phi_{m,eff}$  values of the metals on the HfO<sub>2</sub>/SiO<sub>2</sub> stack were extracted by considering both the interfacial SiO<sub>2</sub> thickness (T<sub>SiO2</sub>) and the fixed charge<sup>[29]</sup>.

#### **3. RESULTS AND DISCUSSION**

Fig. 1(a) shows a plot of the EOT versus  $T_{HfO2}$ . The  $T_{HfO2}$  values were determined by XRR, as shown in Fig. 1(b). The relation between EOT and  $T_{HfO2}$  is given by

$$EOT = \frac{\varepsilon_{SiO_2}}{\varepsilon_{HfO_2}} T_{HfO_2} + T_{SiO_2}$$

(1)

where  $\varepsilon_{SiO_2}$  and  $\varepsilon_{HfO_2}$  are the dielectric constants of SiO<sub>2</sub> and HfO<sub>2</sub>, respectively. Therefore, from the slope and the intercept of a linear fit to the plot of the EOT versus  $T_{HfO_2}$ , the  $\varepsilon_{HfO_2}$  and  $T_{SiO_2}$  values can be respectively extracted by Eq. (1).  $\varepsilon_{HfO_2}$  was ~18 and  $T_{SiO_2}$  was ~1 nm. The extracted  $\varepsilon_{HfO_2}$  value is nearly the same as the reported value of ALD-HfO<sub>2</sub><sup>[30]</sup>.

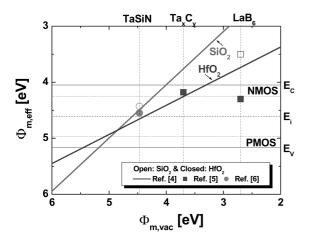

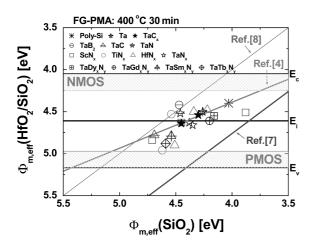

Fig. 2 summarizes the reported  $\Phi_{m,eff}$  versus the metal vacuum workfunction ( $\Phi_{m,vac}$ ) relations. The FLP effect significantly increases the  $\Phi_{m,eff}$  values of HfO<sub>2</sub> devices, especially for metals with very low  $\Phi_{m,vac}$  values. The LaB<sub>6</sub> gates on SiO<sub>2</sub> and HfO<sub>2</sub> show significant extrinsic FLP<sup>[4-6]</sup>. Therefore, compared with SiO<sub>2</sub>, new materials with lower  $\Phi_{m,vac}$  values are necessary for NMOS devices with HfO<sub>2</sub>. In addition, the suppression of extrinsic FLP is needed for an NMOS-compatible  $\Phi_{m,eff}$  value.

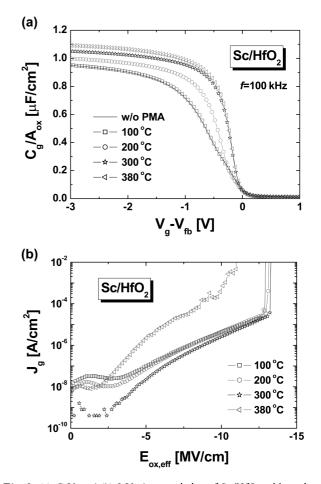

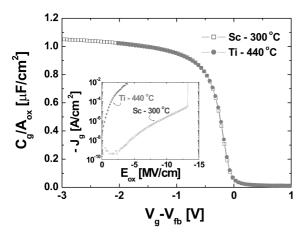

Considering the  $\Phi_{m,vac}$  value of Sc (~ 3.5 eV), the  $\Phi_{m,eff}$  value of Sc on HfO<sub>2</sub> is expected to be appropriate for NMOS devices<sup>[4,31]</sup>. Fig. 3(a) shows the C-V characteristics of the MOS capacitors with Sc gates on ALD-HfO<sub>2</sub> after FG-PMA at various temperatures. The capacitance values in the strong

Table 1. Experiments to obtain the appropriate workfunction

**Fig. 1.** (a) EOT versus  $T_{HrO2}$  plot. From the slope and the intercept,  $\epsilon_{HrO2}$  and  $T_{SiO2}$  respectively can be determined. (b) XRR data of the prepared ALD-HfO2 after O2-PDA at 450 °C for 30 min.

**Fig. 2.** Summary of the reported  $\Phi_{m,eff}$  versus  $\Phi_{m,vac}$  relations. A metal gate with a low  $\Phi_{m,vac}$  value (less than ~4 eV) is needed for an NMOS with HfO<sub>2</sub>. The LaB<sub>6</sub> shows significant extrinsic FLP.

accumulation regime reveal that the EOT decreases as the FG-PMA temperature increases, even at 200 °C. The reduc-

**Fig. 3.** (a) C-V and (b) I-V characteristics of Sc/HfO<sub>2</sub> with various FG-PMA temperatures. EOT decreases above 200  $^{\circ}$ C due to the reactive Sc gate. The leakage current increases above 300  $^{\circ}$ C.

tion of the EOT can be explained by the oxygen-gettering effect of Sc<sup>[17]</sup>. The high oxygen solubility of Sc results in oxygen diffusion from the interfacial SiO<sub>2</sub> layer to the gate electrode. Fig. 3(b) shows the I-V characteristics of the Sc samples. Up to 300 °C, the leakage current density (Jg) in the high electric field (E<sub>ox</sub>=(V<sub>g</sub>-V<sub>fb</sub>)/EOT) regime is nearly unchanged, even though the EOT is decreased. This result suggests that for these annealing conditions the Sc gate has no effect on the quality of the HfO<sub>2</sub> film. However, the FG-PMA at 380 °C significantly increases the leakage current. This increase means that the quality of HfO<sub>2</sub> is degraded at 380 °C by the interface reaction<sup>[32]</sup>. A Ti gate can also be used for an oxygen-gettering electrode<sup>[17]</sup>. However, higher temperature is required for the EOT scaling by the Ti gate. As shown in Fig. 4, the Ti gate sample annealed at 440 °C and the Sc gate sample annealed at 300 °C show a comparable reduction in the EOT ( $\Delta$ EOT=3Å). Although both samples show the same EOT, the leakage current of the Ti sample is significantly higher than that of the Sc sample, as shown in the inset figure of Fig. 4. As with the Sc gate, the Ti

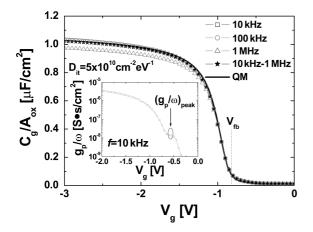

Fig. 4. C-V and G-V characteristics of  $Sc/HfO_2$  after FG-PMA at 300 °C. The sample shows the excellent interfacial quality.

**Fig. 5.** Electrical characteristics of Sc and Ti gates on HfO<sub>2</sub>. Compared with Ti, the Sc gate reduces EOT without increasing the leakage current.

gate increases the values of J<sub>g</sub> at a relatively high temperature. Therefore, the Sc gate more efficiently decreases the EOT while maintaining low leakage current. Fig. 5 shows the C-V characteristics of the Sc sample after FG-PMA at 300 °C, measured at various frequencies ( $f=\omega/2\pi$ ). It can be seen that the frequency dispersion is negligible in the overall bias range. The slightly lower capacitance values at 1 MHz in the strong accumulation regime can be explained by the series resistance of the substrate and the gate<sup>[33]</sup>. Using the measurement at two frequencies and the three-element equivalent circuit model, a frequency-independent C-V curve can be obtained<sup>[33]</sup>. The corrected capacitances ( $C_{10kHz}$ -1MHz) from the data measured at 10 kHz and 1 MHz were in excellent agreement with the measured capacitances at 10 kHz and 100 kHz, as shown in Fig. 5. In addition to the negligible frequency dispersion, the measured curves were in good agreement with the curve calculated by the quantummechanical (QM) simulation<sup>[28]</sup>. This result means that the

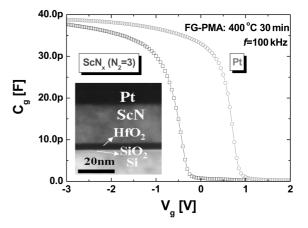

**Fig. 6.** C-V characteristics of Pt and ScN<sub>x</sub> (N<sub>2</sub>=3sccm) gates on 46 Å-HfO<sub>2</sub>. Inset figure shows a TEM image of the ScN<sub>x</sub> sample. The C-V and TEM results suggest that negligible interaction occurs at the ScN<sub>x</sub>/HfO<sub>2</sub> interface.

Sc sample has good interfacial quality. In order to evaluate the interface trap density (D<sub>it</sub>), the G-V characteristics were used, as shown in the inset of Fig. 5. In general, D<sub>it</sub> is proportional to the value of the G<sub>p</sub>/ $\omega$  peak and the extracted value is about 5×10<sup>-10</sup> cm<sup>-2</sup>eV<sup>-1</sup>. As a result, the excellent interfacial quality of the Sc sample can be retained even though the EOT is aggressively reduced. Considering the interfacial layer of the as-deposited sample and the  $\Delta$ EOT value of the annealed sample, the excellent value of D<sub>it</sub> may be due to the remaining interfacial SiO<sub>2</sub> layer near the Si substrate.

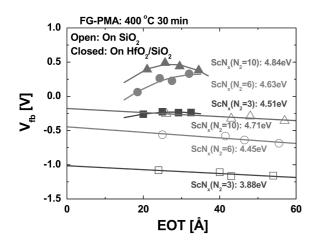

In order to overcome the poor thermal stability and the difficulty of controlling the EOT of the reactive pure metal with a very low workfunction, various reactive-sputtered metal nitrides were evaluated. Fig. 6 shows the stability of  $ScN_x$  at an N<sub>2</sub> flow rate of 3 sccm. The FG-PMA at 400 °C for 30 min was performed after depositing ScN<sub>x</sub> and Pt gates on 46 Å-HfO<sub>2</sub>/SiO<sub>2</sub> stacks. The strong accumulation regime reveals that the capacitance values of the ScNx and Pt devices are nearly the same. The highly similar EOT indicates that a negligible reaction occurs near the interface between ScN<sub>x</sub> and HfO<sub>2</sub>. Examination of a TEM image of the  $ScN_x$  sample, shown in the inset of Fig. 6, confirms the negligible reaction at the ScN<sub>x</sub>/HfO<sub>2</sub> interface. Fig. 7 shows the  $V_{fb}$ -EOT relations of the ScN<sub>x</sub> gates on SiO<sub>2</sub> and HfO<sub>2</sub> with various  $N_2$  flow rates. In the case of the SiO<sub>2</sub> samples, the V<sub>fb</sub> versus EOT relation is given by

$$V_{fb} = \Phi_{m,eff} - \Phi_s - \frac{Q_{fixed}}{\varepsilon_{SiO_2}} EOT$$

<sup>(2)</sup>

where  $\Phi_s$  and  $Q_{fixed}$  are the workfunction of the substrate and the fixed charge in the SiO<sub>2</sub>, respectively. From Eq. (2),  $V_{fb}$ is linearly dependent on the EOT. In Fig. 7, the ScN<sub>x</sub>/SiO<sub>2</sub> samples show that the linear  $V_{fb}$ -EOT relations have nearly the same slope irrespective of the N<sub>2</sub> flow rate. In contrast to

**Fig. 7.** V<sub>fb</sub>-EOT relations of ScN<sub>x</sub> on SiO<sub>2</sub> and HfO<sub>2</sub> after FG-PMA at 400 °C for 30 min. The ScN<sub>x</sub>/SiO<sub>2</sub> samples show a dramatic change of  $\Phi_{m,eff}$  with N<sub>2</sub> flow rate. The ScN<sub>x</sub>/HfO<sub>2</sub> samples show FLP.

the SiO<sub>2</sub> samples, the ScN<sub>x</sub>/HfO<sub>2</sub> samples show polynomial relations. In the case of the HfO<sub>2</sub>/SiO<sub>2</sub> stack, the  $V_{fb}$  versus EOT relation is given by

$$V_{fb} = \Phi_{m,eff} - \Phi_s + \frac{1}{2\varepsilon_{SiO_2}} Q_{hk} EOT^2 - \frac{1}{\varepsilon_{SiO_2}} (Q_{hk/i} + Q_{hk} T_{SiO_2}) EOT + \frac{1}{\varepsilon_{SiO_2}} (\frac{1}{2} Q_{hk/i} T_{SiO_2} + Q_{hk}) T_{SiO_2}$$

(3)

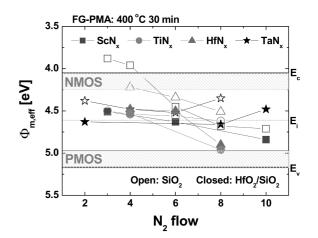

where  $Q_{hk}$  and  $Q_{hk/i}$  are the bulk charge of the HfO<sub>2</sub> and the charge at the interface between HfO<sub>2</sub> and the interfacial SiO<sub>2</sub> layer, respectively<sup>[29]</sup>. Eq. (3) is derived under the assumption that  $Q_{hk}$  and  $Q_{hk/i}$  are significantly higher than the bulk charge of SiO<sub>2</sub> and the SiO<sub>2</sub>/Si interfacial charge, respectively. If  $Q_{hk}$  is negligible, from Eq. (3),  $V_{fb}$  is linearly dependent on the EOT. However, if there is significant Q<sub>hk</sub>, a second-order polynomial fit to the V<sub>fb</sub>-EOT data is necessary for the exact determination of  $\Phi_{m,eff}$ . The  $\Phi_{m,eff}$  values of the ScN<sub>x</sub> gates on both the SiO<sub>2</sub> and HfO<sub>2</sub>/SiO<sub>2</sub> dielectrics were extracted from Eqs. (2) and (3), as shown in Fig. 7. The  $ScN_x/SiO_2$  samples show a wide range of  $\Phi_{m,eff}$  values from ~3.9 eV to ~4.7 eV, and NMOS-compatible  $\Phi_{m,eff}$  values can be obtained. However, the ScN<sub>x</sub>/HfO<sub>2</sub> samples show a relatively narrow range of  $\Phi_{m,eff}$  values from ~4.5 eV to ~4.8 eV, and NMOS-compatible  $\Phi_{m.eff}$  values cannot be obtained. Fig. 8 shows the extracted  $\Phi_{m,eff}$  values of various reactive-sputtered nitrides (ScN<sub>x</sub>, TiN<sub>x</sub>, HfN<sub>x</sub>, and TaN<sub>x</sub>) with the N<sub>2</sub> flow rate. All the tested binary metal nitrides on the HfO<sub>2</sub>/SiO<sub>2</sub> stacks are inappropriate for NMOS devices.

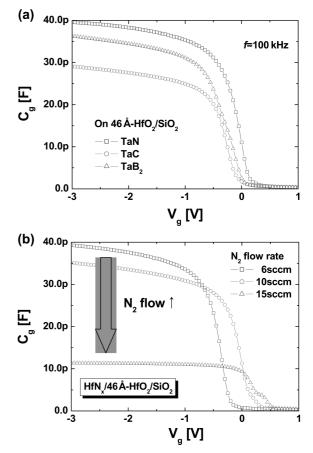

To evaluate the doping effect of metal gates, TaN, TaC, and TaB<sub>2</sub> sputter targets were used. Fig. 9(a) shows the C-V characteristics of the TaN, TaC, and TaB<sub>2</sub> gates on 46 Å-HfO<sub>2</sub>/SiO<sub>2</sub> stacks. In the strong accumulation regime, as shown in Figs. 6 and 9(a), the capacitance values of the TaN sample are nearly the same as those of the Pt sample. How-

Fig. 8.  $\Phi_{m,eff}$  values of binary metal nitrides with various N<sub>2</sub> flow rate. The ScN<sub>x</sub> can be used for NMOS with SiO<sub>2</sub>. In case of HfO<sub>2</sub>, no metal nitride has an appropriate  $\Phi_{m,eff}$  value for NMOS.

**Fig. 9.** C-V characteristics of (a) TaN, TaC, TaB<sub>2</sub>, and (b)  $HfN_x$  gates on 46 Å-HfO<sub>2</sub>. The TaC, TaB<sub>2</sub>, and HfN<sub>x</sub> (N $\geq$ 10sccm) gates increase EOT due to excessive C, B, and N, respectively.

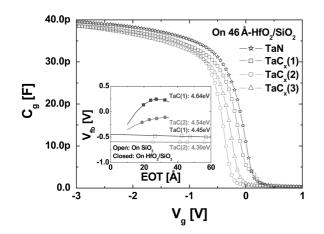

ever, the capacitance values of the TaC and TaB<sub>2</sub> samples are higher than those of the TaN sample. Fig. 9(b) shows the C-V characteristics of  $HfN_x$  gates with various N<sub>2</sub> flow rates. The EOT of the  $HfN_x$  sample rapidly increases with the N<sub>2</sub> flow rate above 10 sccm. The metal HfN has one more electron than needed for a closed shell, and  $Hf_3N_4$  is a dielectric with a closed shell and a band gap<sup>[34]</sup>. Therefore, the EOT of the  $HfN_x$  with an  $N_2$  flow rate above 10 sccm rapidly increases because of excessive nitrogen in the gate. In the same manner, the increased EOT values of the TaC and TaB<sub>2</sub> samples may be due to excessive carbon and boron, respectively. Table 2 summarizes the  $\Phi_{m,eff}$  values of the Ta-based materials (Ta, TaN, TaC and TaB<sub>2</sub>). Considering the  $\Phi_{m,vac}$ values of B (~4.45 eV) and C (~5.0 eV), the excessive boron and carbon may affect the  $\Phi_{m,\text{eff}}$  values of the  $TaB_2$  and TaCgates, respectively<sup>[31]</sup>. In an effort to find a means of avoiding excessive doping of carbon, the reactive-sputtered TaC<sub>x</sub> gates were evaluated with various CH<sub>4</sub>/Ar gas flow rates. As shown in Fig. 10, in contrast to the sample prepared with the TaC target, the EOT values of the reactive-sputtered  $TaC_x$ gates are nearly the same as the EOT of the TaN gate. However, as shown in the inset of Fig. 10, midgap  $\Phi_{m,eff}$  values were obtained for the  $TaC_x/HfO_2$  samples.

In a recent report, lanthanide (Tb, Er, and Yb)-doped nitrides on SiO<sub>2</sub> were used for NMOS-compatible gates<sup>[27]</sup>. To evaluate the lanthanide-doped metal nitrides on ALD-HfO<sub>2</sub>, TaM<sub>x</sub>N<sub>y</sub> (M : Dy, Gd, Sm, Tb) gates were deposited by co-sputtering the TaN target with the lanthanide elements. Fig. 11 shows the C-V characteristics of TaN and TaDy<sub>x</sub>N<sub>y</sub> gates on SiO<sub>2</sub> dielectrics with various thicknesses. In the strong accumulation regime, the capacitance values of the

Table 2.  $\Phi_{m,\text{eff}}$  values of Ta, TaN, TaC, and TaB $_2$  gates on SiO $_2$  and HfO $_2$

| $\Phi_{m,eff} \left[ eV \right]$ | SiO <sub>2</sub> | HfO <sub>2</sub> |

|----------------------------------|------------------|------------------|

| Та                               | 4.26             | 4.50             |

| TaN                              | 4.46             | 4.52             |

| TaC                              | 4.69             | 4.78             |

| $TaB_2$                          | 4.47             | 4.42             |

Fig. 10. C-V and  $V_{fb}$ -EOT characteristics of  $TaC_x$  by reactive sputtering with various  $CH_4/Ar$  gas flow rates. The EOT of the  $TaC_x$  sample was nearly the same as that of the TaN sample.

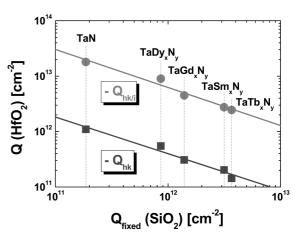

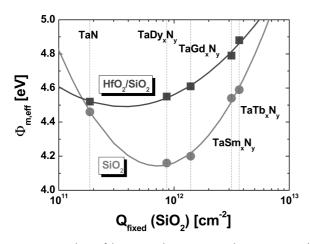

$TaDy_xN_y$  samples are nearly the same as those of the TaN samples. This indicates that the proper addition of Dy does not increase the EOT. The  $TaDy_xN_y$  gates on SiO<sub>2</sub> show a lower  $\Phi_{m,eff}$  value than that of TaN. Fig. 12 shows the values of both Q<sub>fixed</sub> in SiO<sub>2</sub> and Q<sub>hk</sub> and Q<sub>hk/i</sub> in HfO<sub>2</sub>/SiO<sub>2</sub> stacks. The lanthanide elements in the TaM<sub>x</sub>N<sub>y</sub> gates increase the positive Q<sub>fixed</sub> in the SiO<sub>2</sub> samples and decrease the magnitude of the negative  $Q_{hk}$  and  $Q_{hk/i}$  in the HfO<sub>2</sub>/SiO<sub>2</sub> samples, compared with the values of the TaN samples. Therefore, the elements may generate positive charges in both SiO<sub>2</sub> and the  $HfO_2/SiO_2$  stack and compensate the negative charges of the TaN/HfO2 samples. The physical origin of the positive Q<sub>fixed</sub> may be oxygen vacancies in the dielectrics generated by oxygen transport across the metal/oxide interface. The lanthanide elements may strongly attract oxygen due to their high oxygen reactivity. Fig. 13 shows the extracted  $\Phi_{m,eff}$  values of  $TaM_xN_y$  gates versus the values of  $Q_{fixed}$ . In the case of SiO<sub>2</sub>, the  $\Phi_{m,eff}$  values of TaM<sub>x</sub>N<sub>y</sub> are lower than the  $\Phi_{m,eff}$ value of TaN for  $Q_{\text{fixed}}$  values less than  ${\sim}10^{12}\text{cm}^{-2}$  due to the

Fig. 11. C-V characteristics of TaN and TaDy<sub>x</sub>N<sub>y</sub> gates on SiO<sub>2</sub>. The  $\Phi_{m,eff}$  of TaDy<sub>x</sub>N<sub>y</sub> is lower than TaN due to the low  $\Phi_{m,vac}$  of Dy.

**Fig. 12.** For the TaN and  $TaM_xN_y$  samples,  $Q_{hk}$  and  $Q_{hk/i}$  in HfO<sub>2</sub> are plotted with  $Q_{fixed}$  in SiO<sub>2</sub>. The lanthanide elements may generate positive  $Q_{fixed}$  and compensate the negative charges of TaN/HfO<sub>2</sub>.

Fig. 13.  $\Phi_{m,eff}$  values of the TaN and TaM<sub>x</sub>N<sub>y</sub> samples versus  $Q_{fixed}$  in SiO<sub>2</sub>. Compared with the SiO<sub>2</sub> samples, an NMOS-compatible  $\Phi_{m,eff}$  value can not be obtained for the HfO<sub>2</sub>/SiO<sub>2</sub> samples.

Fig. 14.  $\Phi_{m,eff}$  values of all the tested metal gates on HfO<sub>2</sub>/SiO<sub>2</sub> stacks versus on SiO<sub>2</sub>. No metal is appropriate for NMOS devices with HfO<sub>2</sub>.

very low  $\Phi_{m,vac}$  values (~3 eV) of the lanthanide elements<sup>[31]</sup>. Therefore, an NMOS-compatible  $\Phi_{m,eff}$  can be obtained by using the TaM<sub>x</sub>N<sub>y</sub> gates on SiO<sub>2</sub>. However, the excessive oxygen in the TaM<sub>x</sub>N<sub>y</sub> may increase the  $\Phi_{m,eff}$  value for the Q<sub>fixed</sub> above ~10<sup>12</sup> cm<sup>-2</sup>. Compared with SiO<sub>2</sub>, the TaM<sub>x</sub>N<sub>y</sub>/HfO<sub>2</sub> samples show less reduction of the  $\Phi_{m,eff}$  value and an NMOS-compatible  $\Phi_{m,eff}$  cannot be obtained. This may be due to the large amount of transported oxygen in the TaM<sub>x</sub>N<sub>y</sub> gate on HfO<sub>2</sub>.

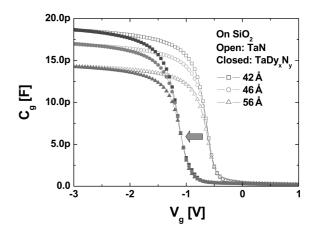

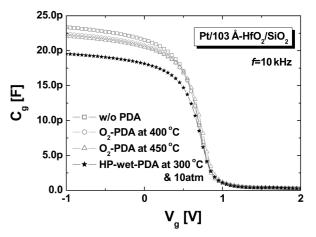

Fig. 14 shows the  $\Phi_{m,eff}$  values of all the tested metal gates. All the metals on the HfO<sub>2</sub>/SiO<sub>2</sub> stack with the conventional O<sub>2</sub>-PDA are inappropriate for NMOS devices. To obtain an NMOS-compatible  $\Phi_{m,eff}$ , we evaluated various surface treatments on ALD-HfO<sub>2</sub>/SiO<sub>2</sub> stacks. Fig. 15 shows the C-V characteristics of Pt gates on 103 Å-HfO<sub>2</sub> dielectrics with conventional O<sub>2</sub>-PDA and HP-wet-PDA processes. The PDA processes increase EOT due to the growth of interfacial

Fig. 15. C-V characteristics of  $Pt/HfO_2$  samples after conventional O<sub>2</sub>-PDA and HP-wet-PDA.

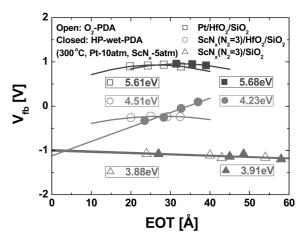

Fig. 16.  $V_{\rm fb}\text{-}EOT$  relations of the Pt and  $ScN_x$  (N<sub>2</sub>=3sccm) gates after O<sub>2</sub>-PDA and HP-wet-PDA. The HP-wet-PDA on the  $ScN_x/HfO_2$  samples results in a dramatic change of  $\Phi_{m,eff}$ .

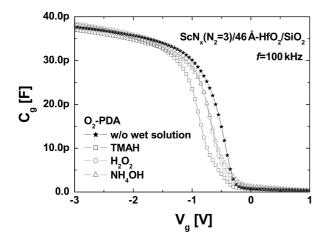

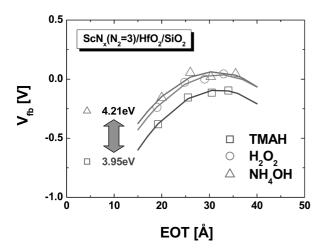

SiO<sub>2</sub>. Fig. 16 shows the  $V_{fb}$ -EOT relations of the Pt and ScN<sub>x</sub> (N<sub>2</sub>=3sccm) samples with conventional O<sub>2</sub>-PDA and HPwet-PDA. For the Pt/HfO<sub>2</sub> and ScN<sub>x</sub>/SiO<sub>2</sub> samples, HP-wet-PDA has a negligible effect on the  $\Phi_{m,eff}$  value. However, the  $\Phi_{m,eff}$  value of the ScN<sub>x</sub> gate on HfO<sub>2</sub> significantly depends on the PDA processes, and the HP-wet-PDA dramatically shifts  $\Phi_{m,eff}$  towards an NMOS-compatible value. Fig. 17 shows the C-V characteristics of ScN<sub>x</sub>/46 Å-HfO<sub>2</sub> samples with various wet-solution (TMAH, H<sub>2</sub>O<sub>2</sub>, and NH<sub>4</sub>OH) treatments after conventional O2-PDA. There is no additional increase of the EOT by the treatments. Fig. 18 shows the V<sub>fb</sub>-EOT relations of the ScN<sub>x</sub>/HfO<sub>2</sub> samples with various wet-solution treatments. As shown in Figs. 16 and 18, all the wet treatments on the HfO<sub>2</sub> surface result in NMOScompatible  $\Phi_{m.eff}$  values between ~3.95 eV and ~4.23 eV. Table 3 summarizes the  $Q_{hk}$  and  $Q_{hk/i}$  values of the ScN<sub>x</sub>/ HfO<sub>2</sub> samples with various wet-solution treatments. The lin-

Fig. 17. C-V characteristics of  $ScN_x/HfO_2$  samples with various wetsolution treatments after O<sub>2</sub>-PDA. The EOT is nearly independent of the wet-solution treatments.

Fig. 18.  $V_{tb}$ -EOT relations of the ScN<sub>x</sub>/HfO<sub>2</sub> samples with various wet-solution treatments. An NMOS-compatible  $\Phi_{meff}$  between ~3.95 eV and ~4.2 eV can be obtained.

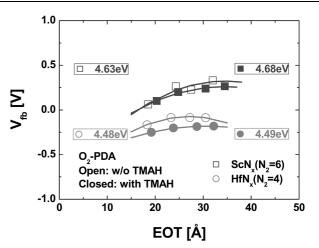

ear V<sub>tb</sub>-EOT relation of the ScN<sub>x</sub>/HfO<sub>2</sub> samples with the HPwet-PDA at 300 °C and 5 atm in Fig. 16, implies a negligible Q<sub>hk</sub>. In addition, the process condition yields the lowest  $|Q_{hk/i}|$ value of ~7×10<sup>12</sup>cm<sup>-2</sup>, which is similar to the value of the Pt/ HfO<sub>2</sub> sample (~6×10<sup>12</sup>cm<sup>-2</sup>). A high Q<sub>hk/i</sub> value is generally observed in the HfO<sub>2</sub>/SiO<sub>2</sub> stack.<sup>29</sup> Fig. 19 shows the V<sub>tb</sub>-EOT relations of the ScN<sub>x</sub> (N<sub>2</sub>=6sccm) and HfN<sub>x</sub> (N<sub>2</sub>=4sccm) gates on HfO<sub>2</sub> with and without TMAH treatments. From Figs. 16, 18, and 19, coexistence of nitrogen deficiency in ScN<sub>x</sub> and oxygen deficiency in HfO<sub>2</sub> might cause significant extrinsic pinning states which might be related to the Sc-Hf bonds at the ScN<sub>x</sub>/HfO<sub>2</sub> interface.

#### 4. CONCLUSIONS

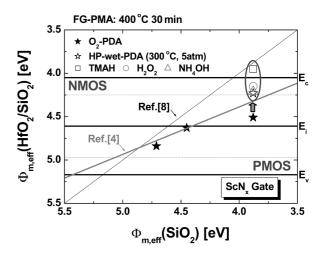

Using both  $ScN_x$  gates and wet surface treatments on ALD-HfO<sub>2</sub>, as shown in Fig. 20, NMOS-compatible  $\Phi_{m,eff}$

**Table 3.**  $Q_{hk}$  and  $Q_{hk/i}$  of the Pt and ScN<sub>x</sub> (N<sub>2</sub>=3sccm) on HfO<sub>2</sub>. The ScN<sub>x</sub> with the HP-wet-PDA at 300 °C and 10 atm results in the excellent quality

| 1 2                                   |                     |             |                      |                      |  |

|---------------------------------------|---------------------|-------------|----------------------|----------------------|--|

| Samples / Charges [cm <sup>-2</sup> ] |                     |             | $\mathbf{Q}_{hk}$    | Q <sub>hk/i</sub>    |  |

| Pt                                    | O <sub>2</sub> -PDA |             | 3.5×10 <sup>11</sup> | 5.7×10 <sup>12</sup> |  |

|                                       | O <sub>2</sub> -PDA |             | 2.2×10 <sup>11</sup> | $3.9 \times 10^{12}$ |  |

| ScN <sub>x</sub>                      | HP-wet-<br>PDA      | 200°C 10atm | 7.5×10 <sup>11</sup> | $1.6 \times 10^{13}$ |  |

|                                       |                     | 300°C 10atm | $1.1 \times 10^{12}$ | $2.5 \times 10^{13}$ |  |

|                                       |                     | 300°C 5atm  | Negligible           | 7.0×10 <sup>12</sup> |  |

|                                       | wet<br>solution     | TMAH        | 7.6×10 <sup>11</sup> | $1.7 \times 10^{13}$ |  |

|                                       |                     | $H_2O_2$    | $7.0 \times 10^{11}$ | $1.5 \times 10^{13}$ |  |

|                                       |                     | NH4OH       | $7.2 \times 10^{11}$ | $1.5 \times 10^{13}$ |  |

Fig. 19.  $V_{rb}$ -EOT relations of the ScN<sub>x</sub> (N<sub>2</sub>=6sccm) and HfN<sub>x</sub> (N<sub>2</sub>=4sccm) gates on HfO<sub>2</sub> with and without TMAH treatment.

Fig. 20. Effect of various wet treatments on the  $\Phi_{m,eff}$  values of ScN<sub>x</sub>. Using ScN<sub>x</sub> gates and wet treatments, NMOS-compatible  $\Phi_{m,eff}$  values can be obtained.

values of  $\sim 4 \text{ eV}$  were obtained. Therefore, the wet treatment is a promising process technology to reduce the extrinsic FLP, especially for NMOS-compatible metal gates.

## ACKNOWLEDGEMENT

This research was supported by System IC 2010. The authors would like to thank Samsung Electronics for providing ALD-HfO<sub>2</sub> samples.

#### REFERENCES

- 1. G. D. Wilk, R. M. Wallace, and J. M. Anthony, *J. Appl. Phys.* **89**, 5243 (2001).

- M. Gutowski, J. E. Jaffe, C.-L. Liu, M. Stoker, R. I. Hegde, R. S. Rai, and P. J. Tobin, *Appl. Phys. Lett.* 80, 1897 (2002).

- 3. C. C. Hobbs, L. R. C. Fonseca, A. Knizhnik, V. Dhandapani, S. B. Samavedam, W. J. Taylor, J. M. Grant, L. G. Dip, D. H. Triyoso, R. I. Hegde, D. C. Gilmer, R. Garcia, D. Roan, M. L. Lovejoy, R. S. Rai, E. A. Hebert, H.-H. Tseng, S. G. H. Anderson, B. E. White, and P. J. Tobin, *IEEE Trans. Electron Devices* **51**, 971 (2004).

- 4. Y.-C. Yeo, T.-J. King, and C. Hu, J. Appl. Phys. 92, 7266 (2002).

- J. K. Schaeffer, C. Capasso, L. R. C. Fonseca, S. Samavedam, D. C. Gilmer, Y. Liang, S. Kalpat, B. Adetutu, H.-H. Tseng, Y. Shiho, A. Demkov, R. Hegde, W. J. Taylor, R. Gregory, J. Jiang, E. Luckowski, M. V. Raymond, K. Moore, D. Triyoso, D. Roan, B. E. White, Jr. and P. J. Tobin, *Tech. Dig. Int. Electron Devices Meet.* **2004**, 287 (2004).

- S. B. Samavedam, L. B. La, P. J. Tobin, B. White, C. Hobbs, L. R. C. Fonseca, A. A. Demkov, J. Schaeffer, E. Luckowski, A. Martinez, M. Raymond, D. Triyoso, D. Roan, V. Dhandapani, R. Garcia, S. G H. Anderson, K. Moore, H. H. Tseng, C. Capasso, O. Adetutu, D. C. Gilmer, W. J. Taylor, R. Hegde, and J. Grant, *Tech. Dig. – Int. Electron Devices Meet.* 2003, 307 (2003).

- J. Lee, Y.-S. Suh, H. Lazar, R. Jha, J. Gurganus, Y. Lin, and V. Misra, *Tech. Dig. – Int. Electron Devices Meet.* 2003, 323 (2003).

- S. Zafar, V. Narayanan, A. Callegari, F. R. McFeely, P. Jamison, E. Gusev, C. Cabral, and Jr. R. Jammy, *Symposium on VLSI Technology Digest*, p. 44 (2005).

- C. Hobbs, L. Fonseca, V. Dhandapani, S. Samavedam, B. Taylor, J. Grant, L. Dip, D. Triyoso, R. Hegde, D. Gilmer, R. Garcia, D. Roan, L. Lovejoy, R. Rai, L. Hebert, H. Tseng, B. White, and P. Tobin, *Symposium on VLSI Technology Digest*, p. 9 (2003)

- E. Cartier, V. Narayanan, E. P. Gusev, P. Jamison, B. Linder, M. Steen, K. K. Chan, M. Frank, N. Bojarczuk, M. Copel, S. A. Cohen, S. Zafar, A. Callegari, M. Gribelyuk, M. P. Chudzik, C. Cabral Jr., R. Carruthers, C. D'Emic, J. Newbury, D. Lacey, S. Guha, and R. Jammy, *Symposium on VLSI Technology Digest*, p. 44 (2004).

- K. Xiong, P. W. Peacock, and J. Robertson, *Appl. Phys. Lett.* 86, 012904 (2005).

- M. S. Joo, B. J. Cho, N. Balasubramanian, and D.-L. Kwong, IEEE Electron Device Lett. 25, 716 (2004).

- K. Shiraishi, K. Yamada, K. Torii, Y. Akasaka, K. Nakajima, M. Kohno, T. Chikyo, H. Kitajima, and T. Arikado, *Symposium on VLSI Technology Digest*, p. 108 (2004).

- 14. H. Takeuchi, H. Y. Wong, D. Ha, and T.-J. King, Tech. Dig.

- Int. Electron Devices Meet. 2004, 829 (2004).

- 15. E. Cartier, F. R. McFeely, V. Narayanan, P. Jamison, B. P. Linder, M. Copel, V. K. Paruchuri, V. S. Basker, R. Haight, D. Lim, R. Carruthers, T. Shaw, M. Steen, J. Sleight, J. Rubino, H. Deligianni, S. Guha, R. Jammy, and G. Shahidi, *Symposium on VLSI Technology Digest*, p. 230 (2005).

- V. Misra, G. P. Heuss, and H. Zhong, *Appl. Phys. Lett.* 78, 4166 (2001).

- 17. H. Kim, P. C. McIntyre, C. O. Chui, K. C. Saraswat, and S. Stemmer, *J. Appl. Phys.* **96**, 3467 (2004).

- H. Zhong, S.-N. Hong, Y.-S. Suh, H. Lazar, G. Heuss, and V. Misra, *Tech. Dig. – Int. Electron Devices Meet.* 2001, 467 (2001).

- 19. B.-Y. Tsui, and C.-F. Huang, *IEEE Electron Device Lett.* 24, 153 (2003).

- 20. I. Polishchuk, P. Ranade, T.-J. King, and C. Hu, *IEEE Electron Device Lett.* 23, 200 (2002).

- 21. Y. Akasaka, K. Miyagawa, A. Kariya, H. Shoji, T. Aoyama, S. Kume, M. Shigeta, O. Ogawa, K. Shiraishi, A. Uedono, K. Yamabe, T. Chikyow, K. Nakajima, M. Yasuhira, K. Yamada, and T. Arikado, *Extended Abstracts of the International Conference on Solid State Devices and Materials*, p. 196, Tokyo (2004).

- 22. C. Ren, H. Y. Yu, J. F. Kang, Y. T. Hou, M.-F. Li, W. D. Wang, D. S. H. Chan, and D.-L. Kwong, *IEEE Electron Device Lett.* 25, 123 (2004).

- 23. J. Westlinder, T. Schram, L. Pantisano, E. Cartier, A. Kerber, G. S. Lujan, J. Olsson, and G. Groeseneken, *IEEE Electron Device Lett.* 24, 550 (2003).

- 24. H. Y. Yu, J. F. Kang, C. Ren, J. D. Chen, Y. T. Hou, C. Shen, M. F. Li, D. S. H. Chan, K. L. Bera, C. H. Tung, and D.-L. Kwong, *IEEE Electron Device Lett.* 25, 70 (2004).

- 25. Y.-S. Suh, G. P. Heuss, J.-H. Lee, and V. Misra, *IEEE Electron Device Lett.* 24, 439 (2003).

- 26. J. K. Schaeffer, S. B. Samavedam, D. C. Gilmer, V. Dhandapani, P. J. Tobin, J. Mogab, B.-Y. Nguyen, B. E. White, Jr., S. Dakshina-Murthy, R. S. Rai, Z.-X. Jiang, R. Martin, M. V. Raymond, M. Zavala, L. B. La, J. A. Smith, R. Garcia, D. Roan, M. Kottke, and R. B. Gregory, *J. Vac. Sci. Technol.* B **21**, 11 (2003).

- 27. C. Ren, D. S. H. Chan, Faizhal B. B., M.-F. Li, Y.-C. Yeo, A. D. Trigg, A. Agarwal, N. Balasubramanian, J. S. Pan, P. C. Lim, and D.-L. Kwong, *Symposium on VLSI Technology Digest*, p. 42 (2005).

- 28. K. Yang, Y.-C. King, and C. Hu, Symposium on VLSI Technology Digest, p. 77 (1999).

- 29. R. Jha, J. Gurganos, Y. H. Kim, R. Choi, J. Lee, and V. Misra, *IEEE Electron Device Lett.* 25, 420 (2004).

- 30. J.-C. Lee, S.-J. Oh, M. Cho, C. S. Hwang, and R. Jung, *Appl. Phys. Lett.* 84, 1305 (2004).

- 31. H. B. Michaelson, J. Appl. Phys. 48, 4729 (1977).

- 32. K. Takahashi, K. Manabe, A. Morioka, T. Ikarashi, T. Yoshihara, H. Watanabe, and T. Tatsumi, *Extended Abstracts of the International Conference on Solid State Devices and Materials*, p. 22, Tokyo (2004).

- 33. K. J. Yang and C. Hu, *IEEE Trans. Electron Devices* **46**, 1500 (1999).

- 34. G. Shang, P. W. Peacock, and J. Robertson, *Appl. Phys.* Lett. **84**, 106 (2004).